During last month’s HPC-AI Advisory Council conference, AMD’s Martin Hilgeman (Sr. Manager, HPC Applications) held a presentation that offered new insight on the company’s next-generation architectures for the datacenter, Milan (Zen 3) and Genoa (Zen 4).

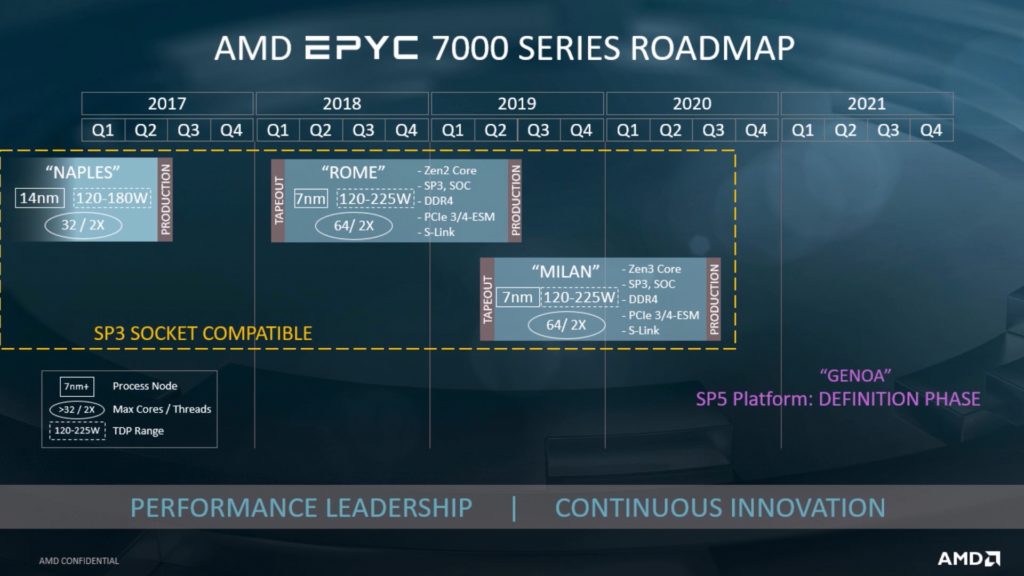

According to AMD’s EPYC 7000 roadmap, Milan will adopt the same SP3 server socket and mirror Rome’s (Zen 2) core/thread count (which dispels earlier reports about a 4x SMT implementation), TDP, memory support (DDR4), and PCIe configurations. The implication is that Zen 3’s performance improvements will likely come from IPC enhancements and clock speed gains.

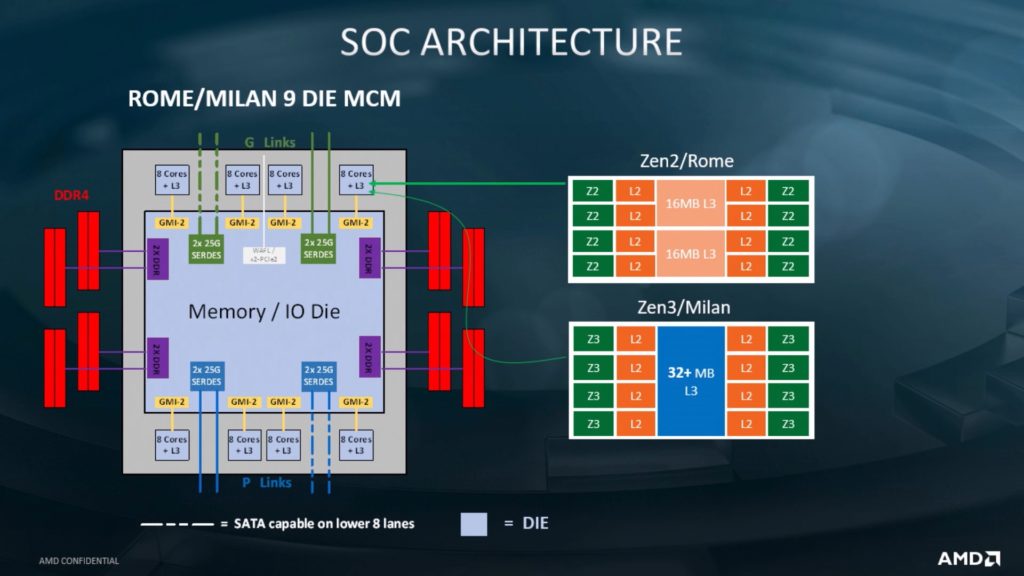

Diagrams also reveal that Zen 3 will have a different L3 cache setup. Unlike Zen 2, which featured two 16 MB L3 caches, Zen 3 will use one larger L3 cache 32+ MB in size. OC3D says this change will result in lower latencies between CPU cores and improved access to the onboard memory.

Hilgeman had less to say about Zen 4, but he did reveal it would require a new socket (SP5), support DDR5, and offer “new capabilities.” Genoa remains in the design phase.

Zen 3 will mark another major design change for AMD’s Zen CPU architecture, offering changes what will be hugely beneficial for the processor’s internal cache latencies. While little is known about AMD’s Zen 3 core design, these slides show us that AMD’s next-generation architecture aims to mitigate more of the shortcomings of AMD’s existing designs. These downsides were already largely reduced with Zen 2, but Zen 3 seeks to take things to another level.