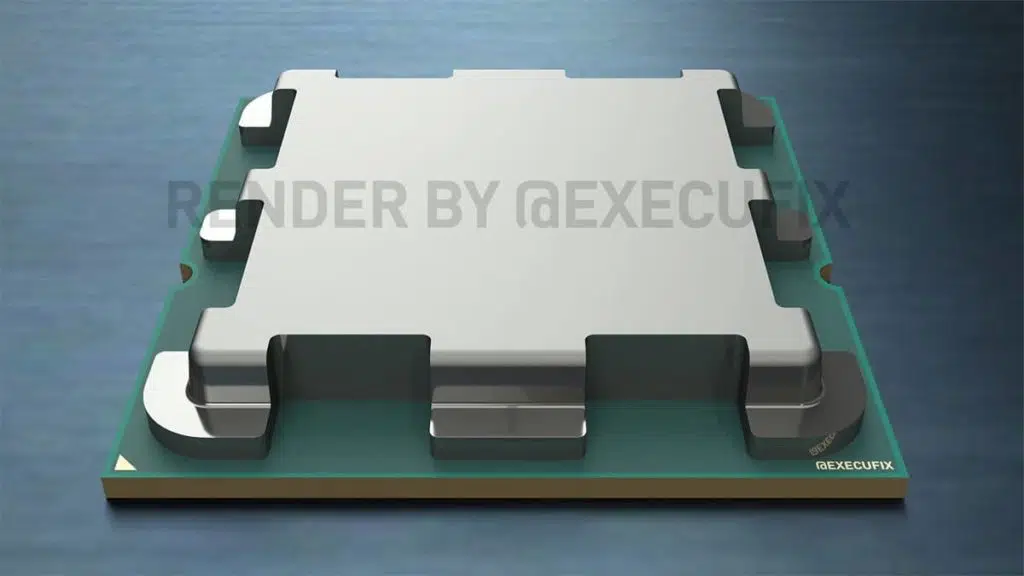

AMD’s upcoming family of Zen 4-based Ryzen 7000 Series processors (code name “Raphael”) will be some of the first to leverage red team’s new AM5 platform, which switches out its predecessor’s PGA (pin grid array) design for an LGA (land grid array) one that shifts the pins over to the socket (LGA 1718). According to new renders shared by leaker ExecutableFix, these chips will also introduce a brand-new IHS (integrated heat spreader) design that replaces the traditional square metal lid with one that features multiple notches and cutouts. It isn’t yet clear what prompted AMD to redesign the exterior cover for its Zen 4 processors so significantly.

This is how Raphael will look like from the top. AM5 sure has an interesting design 🤔

— ExecutableFix (@ExecuFix) May 30, 2021

This took me some time to make and I'm quite pleased with the end result 💥 pic.twitter.com/TiWpE1VXQZ

AMD CPUs for AM5 socket would allegedly support dual-channel DDR5 memory as well as PCIe Gen4.0. This means that there would no Gen5 support and that would remain exclusive to Alder Lake-S, at least for the time being. The Raphael CPUs will have 28 PCIe lanes, which is an upgrade of 4 compared to Zen3 CPUs. At this time, AMD is planning 120W CPUs for this socket, but there are allegedly plans for 170W SKUs as well.

Sources: ExecutableFix, VideoCardz